大家好,我是痞子衡,是正经搞技术的痞子。今天痞子衡给大家介绍的是飞思卡尔i.MX RTyyyy系列EVK在串行nor Flash调试的原理。

本文是i.MXRT硬件那些事系列第二篇的续集,在第二篇首集中痞子衡给大家详细介绍了EVK板载调试器用法,有了调试器在手,从此调试不用愁。从调试代码所在目标存储器类别上来分,调试一般分为在SRAM调试和在Flash调试。在SRAM调试实现比较简单,程序直接从JTAG/SWD口灌进RAM即可;在Flash调试,则相对复杂一点,因为首先需要有Flash下载算法,下载成功后才能调试。

通常的Cortex-M内核MCU一般都会内嵌并行nor Flash,这个并行nor Flash是直接挂在Cortex-M内核高性能AHB总线上的,知名IDE如果支持这款MCU,也都会同时集成对应Flash的下载算法,方便用户直接在IDE里下载代码进Flash和XIP调试,但是i.MXRT内部并没有Flash,用户需要自己外接Flash,那该怎么办?还能在线XIP调试么?别着急,i.MXRT可以支持外接并行nor和串行nor实现XIP,从节省管脚数的角度,最常见的做法是将串行nor Flash挂在i.MXRT FlexSPI总线上,FlexSPI支持XIP特性,所以原理上可以实现在线调试,今天痞子衡就为大家介绍i.MXRT上在外部串行Flash调试的原理:

一、ARM CoreSight调试架构

要实现在串行Flash调试,首先要能对内核进行调试。i.MXRT芯片是基于Cortex-M内核的,而Cortex内核的调试和跟踪,当然离不开CoreSight,它是ARM公司于2004年推出的一种新的调试体系结构,也是内核授权的一部分。

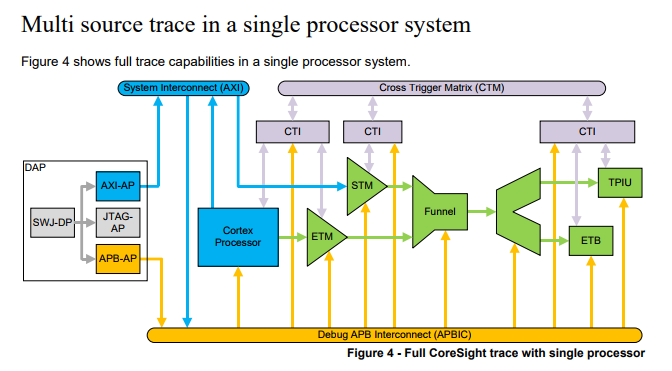

CoreSight功能非常强大,其包含了很多调试组件(即各种协议),下图来自于 CoreSight技术简介手册,图中标出了CoreSight架构下的各种调试组件之间的联系,这么多组件一下子看起来会有点晕,如果我们按功能将这些组件分组,它们可以被分成如下三组:

- 源部件(Source):芯片上跟踪数据的来源,产生跟踪数据发送到ATB(AMBA Trace Bus)。比如STM和ETM都属于Source部分。

- 控制访问部件(Sink):配置和控制数据流的产生,但是不产生数据流,即那些可以保持从Source过来数据的模块。比如DAP和ECT(包含CTI和CTM)都属于Sink部分。

- 汇聚点(Link):芯片上跟踪数据的终点,用于引导从Source到Sink过程中的类似于通道作用的模块。比如TPIU、ETB和SWO都属于汇聚点。

本文主要是概述性地介绍i.MXRT在外部串行Flash调试的原理,并不想深入探析CoreSight,因此对于CoreSight,我们只需要知道是它完成了主要的调试工作,而CoreSight唯一的依赖就是要保证能通过DAP组件从AMBA总线实时访问系统内存和外设寄存器(当然包括外部串行Flash中的代码)。

二、i.MXRT FlexSPI外设特性

要实现在串行Flash调试,其次是代码要能在串行Flash中XIP(原地执行),即cpu要能实时从串行Flash中任意位置取指令和数据。本文讲的串行Flash一般指SPI接口的nor Flash,SPI模式可以是Single/Dual/Quad/Octal。无论是哪种SPI模式,这种接口的Flash本质上都属于串行Flash,地址线和数据线不仅共享而且是串行的。而按照通常的理解,要能够实现XIP,Flash应该是并行总线接口挂在AMBA上,这个并行总线应有独立的地址线和数据线,且地址线宽度跟Flash大小相对应。那么串行Flash为什么能在i.MXRT上实现XIP呢?答案就是FlexSPI外设。

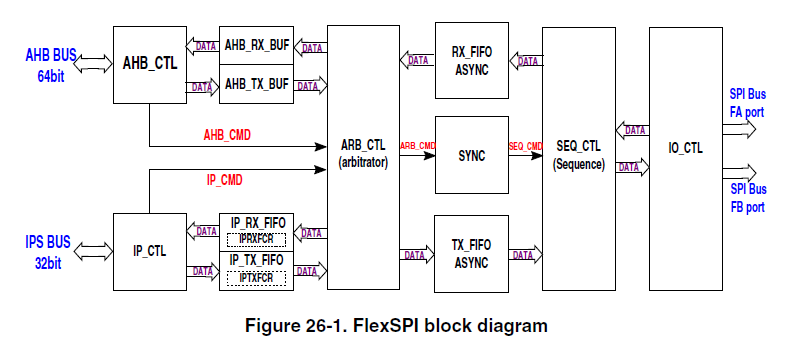

让我们打开RT1050参考手册,找到FlexSPI外设章节,可以看到如下FlexSPI模块框图,框图右边是FlexSPI与外部串行Flash的信号连接,框图左边是FlexSPI与i.MXRT系统内部总线连接,总线连接分为两种,分别是32bit IPS BUS(即手动操作FlexSPI寄存器发送Flash读写命令),64bit AHB BUS(由FlexSPI翻译AHB访问地址并自动发送相应Flash读写命令),串行Flash能够XIP的奥秘就在FlexSPI外设的AHB BUS连接。

关于这个64bit AHB BUS连接,我们可以FlexSPI特性里的Memory mapped read/write access by AHB Bus一栏找到更多细节。i.MXRT为FlexSPI外设在系统内存里分配了AHB访问地址映射(对于XIP调试来说主要是读访问),当cpu取指到FlexSPI AHB地址映射空间时,FlexSPI外设会自动完成从外部串行Flash读取指令数据的工作,并将指令数据存放到AHB RX buffer里(一共8个),cpu直接从AHB RX buffer里获取指令去执行,AHB RX buffer可以有效降低读延时。

- AHB RX Buffer implemented to reduce read latency. Total AHB RX Buffer size: 128 x 64 Bits

- 16 AHB masters supported with priority for read access

- 8 flexible and configurable buffers in AHB RX Buffer

- AHB TX Buffer implemented to buffer all write data from one AHB burst. AHB TX Buffer size: 8 x 64 Bits

- All AHB masters share this AHB TX Buffer. No AHB master number limitation for Write Access.

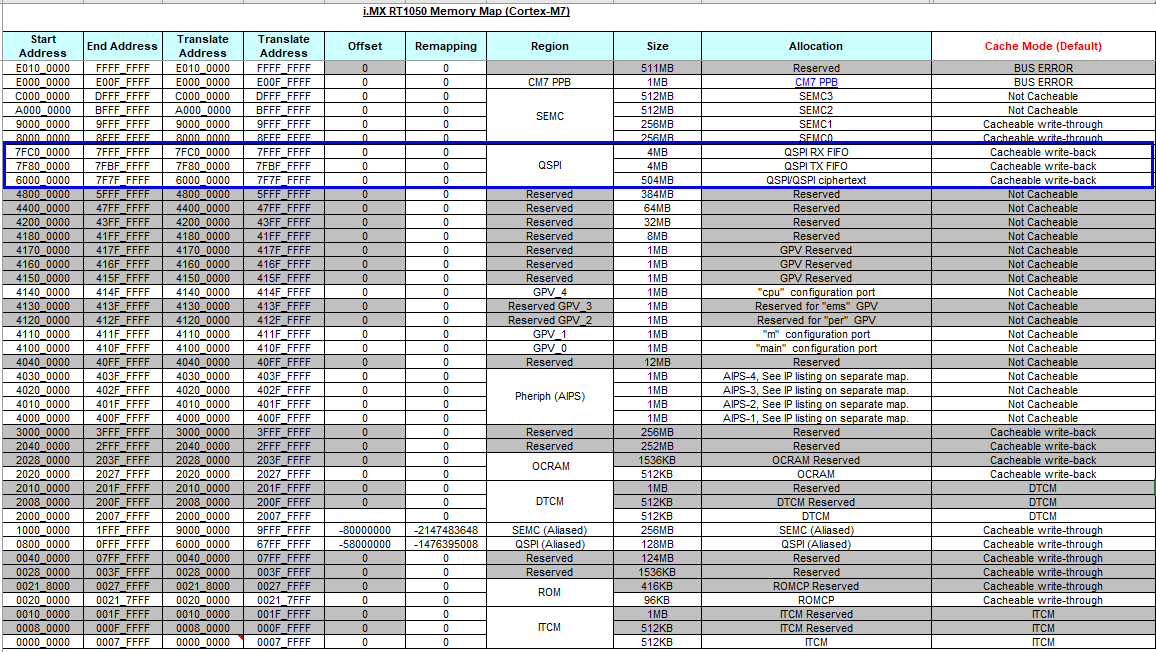

关于FlexSPI AHB地址映射,可见下面的RT1050 memory map表,AHB映射起始地址为0x60000000,最大支持504MB的空间(适用RT1010/RT1020/RT1050/RT1060)。如果是RT1064,AHB映射起始地址改为0x70000000;如果是RT1170,除了0x60000000映射地址外还新增了0x30000000的地址映射。FlexSPI AHB映射地址读访问包含以下特点:

- Cachable and Non-Cachable access

- Prefetch Enable/disable

- Burst size: 8/16/32/64 bits

- All burst type: SINGLE/INCR/WRAP4/INCR4/WRAP8/INCR8/WRAP16/INCR16

三、串行nor Flash下载算法

要实现在串行Flash调试,最后要确保代码被成功下载到串行Flash中。串行Flash的读写不像访问RAM那样简单,是需要一套专门的FlexSPI nor Flash驱动的,即所谓的Flash下载算法。

串行Flash种类很多,虽然大多都符合JESD216标准,但是具体到某个厂家生产的Flash,还是有细微区别的。有的Flash下载算法力求支持尽可能多的Flash,而有的Flash下载算法则仅针对某个系列Flash。不管是哪种Flash下载算法,对于i.MXRT这样没有内部Flash的芯片而言,Flash下载算法都是要跟具体的i.MXRT开发板相关联的,因为开发板决定了Flash连接的pinmux,Flash下载算法里FlexSPI管脚初始化要与开发板相匹配。

每个IDE的Flash下载算法设计不尽相同,本文暂不详细介绍具体Flash下载算法,后续文章会对常见IDE的Flash下载算法设计进行详解。

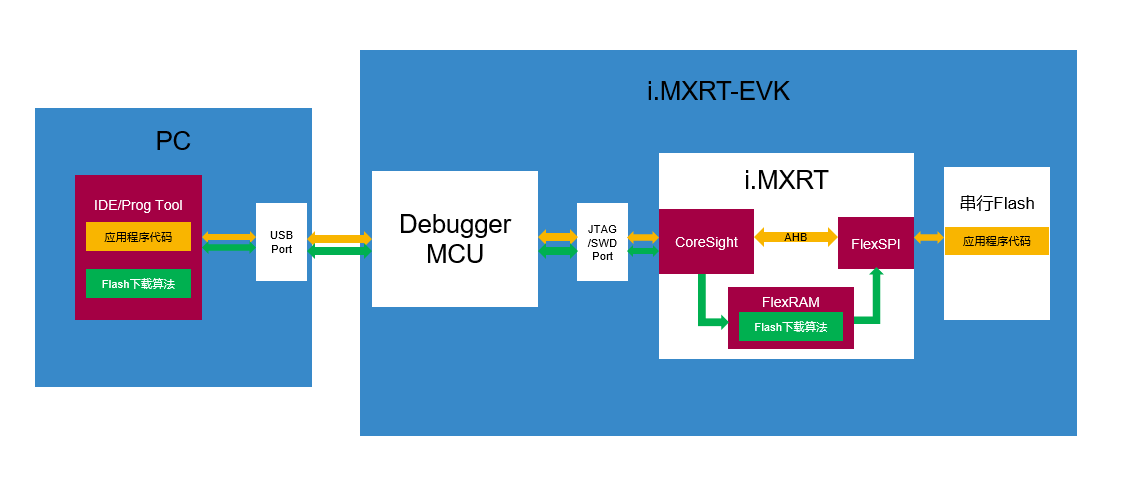

四、在串行Flash调试过程

CoreSight架构,FlexSPI特性,nor Flash下载算法都介绍过了,在串行Flash调试的充分条件都有了。现在痞子衡为大家综合介绍一下调试过程。下面是痞子衡特地画的简图,其实调试过程概述起来并不复杂,当你启动IDE调试时,预先放在IDE里的Flash下载算法(可执行文件)会首先通过调试器下载到i.MXRT内部FlexRAM中运行,并完成FlexSPI外设初始化和应用程序下载工作(将应用程序可执行文件下载进串行Flash中),应用程序下载完成之后,便由CoreSight开始接管调试工作,此时cpu已经可以通过AHB总线访问挂在FlexSPI外设上的串行Flash里的代码,所以CoreSight当然可以完成实时代码运行控制与跟踪,你在IDE里也就可以进行单步调试啦。

至此,飞思卡尔i.MX RTyyyy系列EVK在串行nor Flash调试的原理痞子衡便介绍完毕了,掌声在哪里~~~

版权声明:本文内容由互联网用户自发贡献,该文观点与技术仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 [email protected] 举报,一经查实,本站将立刻删除。